# **CONHECIMENTOS ESPECÍFICOS**

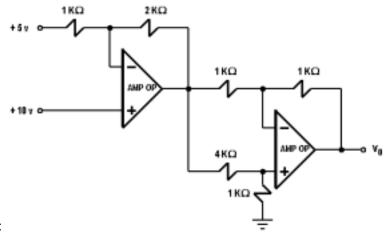

CONSIDERE AS CONVENÇÕES UTILIZADAS NA ELABORAÇÃO DAS QUESTÕES

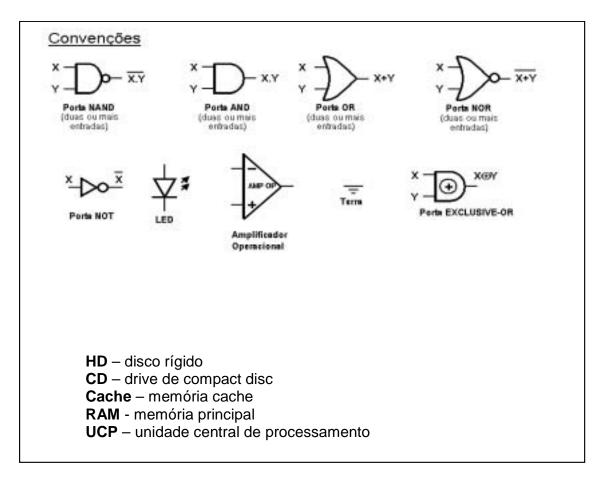

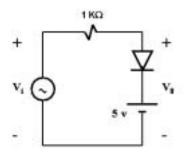

26. Observe o circuito mostrado abaixo.

Considerando-se os diodos ideais, o valor da tensão  $V_{_{0,}}$  em volts, é:

- A) 4

- B) 3

- C) 2

- D) 1

- E) 0

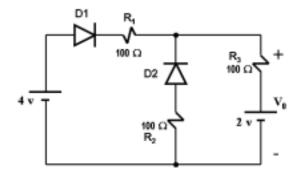

27. Considere o circuito mostrado abaixo.

Se  $V_{BE} = 0$  e  $\beta = 0$  = 100, o ponto de operação ( $V_{CE}$ ,  $I_{C}$ ), respectivamente em (volts, mA) é:

- A) 4/4

- B) 6/3

- C) 0/6

- D) 8 / 2

- E) 6/4

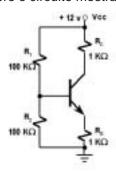

28. Considere o circuito mostrado abaixo.

O valor de V<sub>0</sub>, em volts, é:

- A) + 5

- B) + 3

- C) 10

- D) 5

- E) 12

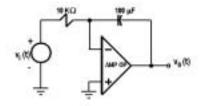

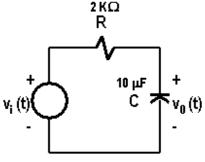

29. Observe o circuito abaixo.

Considerando-se que a entrada  $v_i$  é uma rampa  $(v_i(t) = t)$ , ao final de 1 segundo a saída  $v_0$ , em volts, será:

- A) + 1

- B) 1

- C) + 0.5

- D) 0.5

- E) + 2

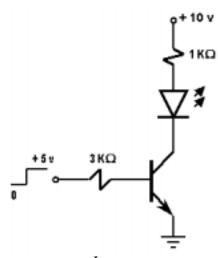

30. O circuito abaixo é um comando de LED. Este se acende quando nele são aplicados 2 volts.

Se

$$V_{BE} = V_{CE_{saturacao}} = 0$$

e  $\beta = \frac{I_C}{I_B} = 100$ , pode-se afirmar que, quando a entrada vai a + 5 volts, o LED:

- A) se acende e o transistor está na região ativa

- B) se acende e o transistor está saturado

- C) se acende, mas é impossível prever o estado do transistor

- D) não se acende e o transistor está cortado

- E) não se acende, mas é impossível prever o estado do transistor

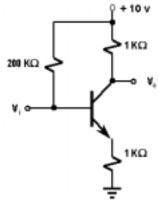

- 31. Considere o circuito mostrado abaixo.

A máxima excursão de sinal no coletor será alcançada se o ponto de operação  $(V_{CE}, I_C)$  do transistor for, respectivamente em volts e mA:

- A) 5/5

- B) 10 / 0

- C) 5 / 2.5

- D) 0/5

- E) 3/3.5

- 32. Comparando-se os diodos retificadores e os diodos zeners, pode-se afirmar que:

- A) Em polarização direta, ambos apresentam comportamento semelhante; em polarização inversa, ambos apresentam sempre comportamentos diferente.

- B) Em polarização inversa, ambos apresentam comportamento semelhante; em polarização direta, ambos sempre apresentam comportamento diferente.

- C) Em polarização inversa, para tensões maiores em módulo do que a tensão de zener, ambos apresentam o mesmo comportamento.

- D) Em polarização inversa, em módulo entre zero volts e a tensão de zener, ambos apresentam o mesmo comportamento.

- E) Em polarizações direta ou inversa, apresentam sempre comportamentos diferentes.

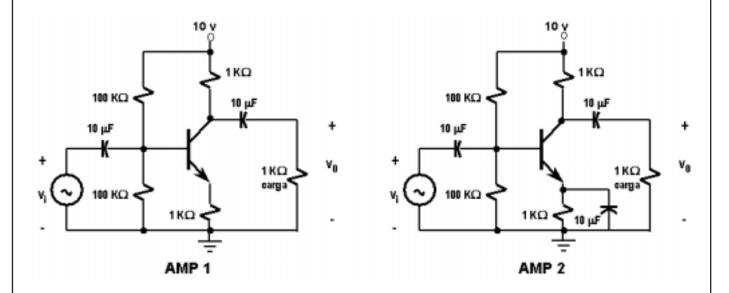

33. Observe, abaixo, os esquemas de dois amplificadores.

$\text{Comparando-se o ganho}\left(\frac{V_0}{V_i}\right) \text{ dos dois amplificadores, onde } \beta = \frac{I_C}{I_B} \text{ são iguais, pode-se afirmar, quanto aos }$

módulos do ganho, que:

- A) são iguais, pois o capacitor de emissor não afeta o ganho

- B) o do AMP 1 é maior, pois o capacitor de emissor do AMP 2 retira um termo multiplicativo do numerador do ganho

- C) o do AMP 2 é maior, pois o capacitor de emissor do AMP 2 retira um termo aditivo do denominador do ganho

- D) não é possível prever o ganho maior, pois não foi dado o valor de  $\beta$

- E) são iguais, pois, para sinal AC, o capacitor de emissor se abre e os circuitos ficam iguais

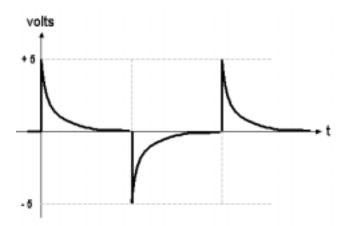

### 34. Considere o gráfico abaixo.

Esse gráfico poderia ser o da tensão em cima de um:

- A) resistor, porém jamais em cima de um capacitor ou de um indutor

- B) resistor ou um indutor, porém jamais em cima de um capacitor

- C) resistor ou um capacitor, porém jamais em cima de um indutor

- D) indutor ou um capacitor, porém jamais em cima de um resistor

- E) resistor ou um capacitor ou um indutor

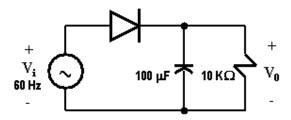

### 35. Considere o circuito mostrado abaixo.

Se a resistência direta do diodo é de 10  $\Omega$ , pode-se afirmar que:

- A) A carga do capacitor é feita pelo diodo com a constante de tempo de 0.001 segundos, muito menor que o período da senóide de entrada.

- B) A carga do capacitor é feita pelo resistor com a constante de tempo de 1 segundo, muito maior que o período da senóide de entrada.

- C) O sinal resultante V<sub>0</sub> apresenta um período igual à metade do período da senóide de entrada.

- D) O sinal resultante V<sub>0</sub> apresenta um período igual ao dobro do período da senóide de entrada.

- E) A constante de tempo de descarga é muito rápida, então devemos esperar um ripple maior que 10%.

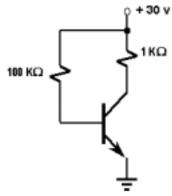

#### 36. Observe o circuito abaixo.

Se o transistor apresenta  $V_{BE}=0$ ,  $\beta=\frac{I_C}{I_B}=50$  e  $P_{MAX}=\frac{1}{8}W$ , pode-se afirmar que, se injetarmos um sinal

AC na base, o transistor:

- A) operará com máxima excursão de sinal no coletor, mas provavelmente queimará

- B) operará normalmente, mas sem máxima excursão de sinal no coletor

- C) operará normalmente, mas muito perto da saturação

- D) provavelmente queimará, por operar muito perto da saturação

- E) operará normalmente com máxima excursão de sinal no coletor

- 37. Em um circuito baseado em JFET, obteve-se a tabela abaixo, onde  $V_{GS}$  é a tensão gate-source e  $I_{D}$  é a corrente de dreno.

| v <sub>GS</sub><br>(volts) | 0  | -0.6 | -1.2 | -1.8 | -3.0 | -4.0 | -5.2 |

|----------------------------|----|------|------|------|------|------|------|

| I <sub>D</sub> (mA)        | 10 | 7.8  | 5.9  | 4.3  | 1.8  | 0.5  | 0    |

Se  $i_{D} = I_{DSS} \bigg( 1 - \frac{v_{GS}}{V_{p}} \bigg)^{2}$ , os valores de  $I_{DSS}$  e de  $V_{p}$  são, em mA e volts, respectivamente:

- A) 0.5 / -0.6

- B) 1.8 / -1,2

- C) 4.3 / -1.8

- D) 7.8 / -4.0

- E) 10 / -5.2

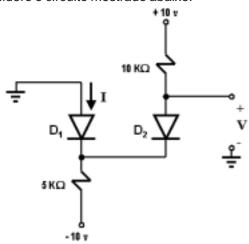

38. Considere o circuito mostrado abaixo.

Supondo-se os diodos ideais, os valores de I e V são, em mA e volts, respectivamente:

- A) 1/0

- B) 0 / 1

- C) 0 /  $\frac{4}{3}$

- D) 2 / 10

- E) 3 / 0

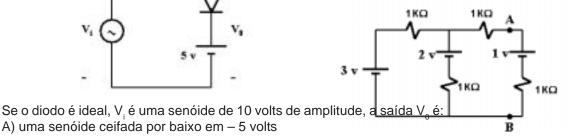

39. Observe o esquema abaixo.

A) uma senóide ceifada por baixo em - 5 volts

- B) uma senóide ceifada por cima em + 5 volts

- C) uma senóide ceifada por cima em 5 volts

- D) uma senóide ceifada por cima em + 5 volts e ceifada por baixo em 5 volts

- E) uma senóide ceifada por baixo em + 5 volts

- 40. Considere o circuito mostrado abaixo.

O equivalente Thevenin aplicado aos pontos A e B apresenta uma fonte:

- A) de 1 volt, em paralelo com a resistência de 1 K $\Omega$

- B) de 2.5 volts, em série com a resistência de 1.5 K $\Omega$

- C) de 1 volt, em série com a resistência de 1,5 K $\Omega$

- D) de 2.5 volts, em série com a resistência de 1 K $\Omega$

- E) de 2.5 volts, em paralelo com a resistência de 1.5 K $\Omega$

41. Observe, abaixo, os esquemas de dois circuitos, A e B.

20 KΩ

5 ΚΩ

1 H

Se  $v_i(t)$  é uma onda quadrada simétrica de período 20 segundos, pode-se afirmar, quanto às respostas  $v_0(t)$  dos circuitos A e B, que:

- A) ambas tem a mesma constante de tempo e ambas respostas  $v_0(t)$  se aproximam de uma onda quadrada

- B) a constante de tempo do circuito A é o dobro da constante de tempo do circuito B

- C) a resposta  $v_0(t)$  do circuito A se aproxima de uma onda quadrada, mas a resposta  $v_0(t)$  do circuito B se aproxima de uma onda triangular

- D) a resposta  $v_0(t)$  do circuito A se aproxima de uma onda triangular, mas a resposta  $v_0(t)$  do circuito B se aproxima de uma onda quadrada

- E) a constante de tempo do circuito A é a metade da constante de tempo do circuito B

- **42**. A função lógica f(A, B, C, D), onde A é o bit mais significativo, apresenta os "mintermos" 1, 2, 4, 7, 8, 11, 13 e 14. Pode-se expressar esta função como:

- A) A+B+C+D

- B)

- C)

- D)  $\overline{A} \cdot \overline{B} + \overline{C} \cdot \overline{D}$

- E)  $A \oplus B \oplus C \oplus D$

- **43**. Um sistema de memória de 1 GB, onde cada palavı número de bits do seu registro endereçador:

- A) 26

- B) 27

- C) 28

- D) 29

- E) 30

2Ω

Circuito A

I

Circuite

- **44**. Suponha que numa transmissão só é possível ocorrer, no máximo, um bit errado. Se a transmissão usa Código de Hamming, ao se receber a seqüência 1 0 1 0 1 0 0, a mensagem veio:

- A) certa, e o dado original é 1 1 1 1

- B) errada, e o dado original é 1 0 1 1

- C) certa, e o dado original é 1 1 0 0

- D) errada, e o dado original é 1 1 0 1

- E) certa, e o dado original é 1 0 1 0

- **45**. Em uma transmissão de 20 bits de dados originais, considera-se as três técnicas de proteção de erros de até um bit: paridade, Código de Hamming e CRC de polinômio gerador x<sup>6</sup>+ x + 1. Pode-se afirmar que o overhead de transmissão para as três técnicas é crescente, na seguinte ordem:

- A) Paridade Hamming CRC

- B) Paridade CRC Hamming

- C) Hamming Paridade CRC

- D) Hamming CRC Paridade

- E) CRC Paridade Hamming

- 46. O número em hexadecimal F 3 B 0 equivale ao número em octal:

- A) 141400

- B) 711510

- C) 726244

- D) 2 2 3 1 0 0

- E) 171660

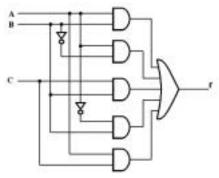

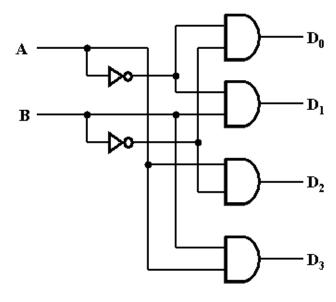

- 47. Considere o circuito lógico representado abaixo.

Esse circuito lógico poderia ser minimizado para:

- A)  $A \cdot B$

- B)

- C)

- D)

- E)

- 48. O número decimal 4102 pode ser expresso pelo número binário:

- A) 1 0 0 0 0 0 0 0 1 1 0 0 0

- B) 1 0 1 0 1 0 1 0 1 0 1 0 0

- C) 1 1 0 0 0 0 1 1 1 1 0 0 0

- D) 100000000110

- E) 1010001000100

- 49. A ordem crescente de tempo de acesso, considerando os dispositivos armazenadores de um computador, é:

**₮**:+**₮**₿.**€**С

- A) RAM cache HD registros internos da UCP CD

- B) HD RAM cache registros internos da UCP

- C) CD HD cache registros internos da UCP RAM

- D) registros internos da UCP cache RAM HD CD

- E) cache registros internos da UCP CD HD RAM

- **50**. Para transmissão telefônica, considera-se as técnicas de multiplexação do canal: FDM, WDM e TDM. Em cada canal e para cada técnica, pode-se afirmar, respectivamente, as seguintes características:

- A) Pode-se transmitir certo tempo em todas as fregüências /

Trata-se da multiplexação por divisão de comprimento de onda /

Pode-se transmitir todo o tempo em certa faixa de freqüências

B) Um canal é definido por faixa específica de frequências /

Trata-se de multiplexação específica para meios não guiados /

Um canal é definido por um conjunto de slots de tempo

C) Pode-se transmitir todo tempo em certa faixa de freqüências e requer circuitos analógicos /

Trata-se de uma variante do FDM para fibras óticas /

Pode-se transmitir em todo espectro, mas só em tempos determinados, e pode ser tratado por circuitos digitais

D) Um canal é definido por um conjunto de slots de tempo /

Trata-se da multiplexação por divisão de comprimento de onda /

Um canal é definido por faixa específica de frequências.

E) Requer circuitos digitais /

É uma variante do TDM para fibras óticas /

Pode ser tratado exclusivamente por circuitos analógicos.

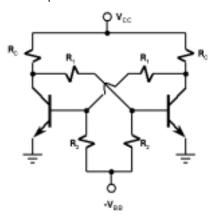

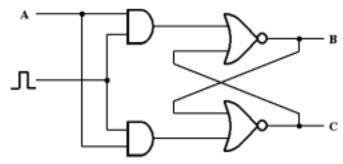

## 51. Observe o esquema abaixo.

O circuito esquematizado acima é a estrutura básica de um:

- A) amplificador operacional

- B) multivibrador biestável

- C) multivibrador monoestável

- D) multivibrador astável

- E) oscilador

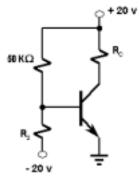

- 52. Observe o esquema abaixo.

Para manter o transistor no corte é preciso que:

- A)  $R_c < 2 K\Omega$

- B)  $R_2 < 50 \text{ K}\Omega$

- C)  $R_2^2 > 50 \text{ K}\Omega$ ;  $R_C < 2 \text{ K}\Omega$

- D)  $R_2 > 50 \text{ K}\Omega$

- E)  $R_c > 2 K\Omega$

- **53**. Se os sinais "+" e "-" de números binários sinalizados são representados, respectivamente, por um bit lógico "0" e um bit lógico "1", o sinal resultante de operações aritméticas de multiplicação ou de divisão pode ser obtido simplesmente entrando os bits de sinal em uma porta:

- A) AND

- B) OR

- C) NAND

- D) NOR

- E) XOR

- 54. Em uma linha "dial up", o modem é um dispositivo que:

- A) conecta diretamente dois computadores usando a linha telefônica

- B) aceita um fluxo de bits seriais na entrada do lado do computador e produz um sinal modulado na saída para a linha telefônica

- C) aceita um fluxo paralelo de bits na entrada do lado do computador e produz sinal modulado na saída para a linha telefônica

- D) é colocado entre o telefone e a central de comutação

- E) dá acesso direto e imediato aos troncos interurbanos de altíssima largura de banda

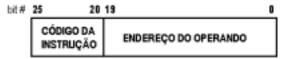

## **55**. Observe a figura abaixo.

Uma instrução de máquina com o formato dado na figura apresenta o número de instruções, número de endereços de memória, dimensão do contador de programa, respectivamente, de:

- A) 32 / 1 mega / 21

- B) 64 / 1 mega / 20

- C) 64 / 2 mega / 21

- D) 32 / 2 mega / 20

- E) 16 / 0.5 mega / 19

## 56. Considere o circuito lógico abaixo.

Esse circuito lógico é uma implementação de um:

- A) multiplexador

- B) comparador

- C) somador

- D) decodificador

- E) deslocador

- 57. Observe o circuito lógico esquematizado abaixo.

Esse circuito lógico é uma implementação de:

- A) um decodificador

- B) um somador

- C) um subtrador

- D) um flip-flop set-reset

- E) uma memória de 1 bit

- 58. Para sinalizar com nível lógico "1", só quando duas entradas forem iguais a "0", pode ser usada uma porta:

- A) AND

- B) OR

- C) NAND

- D) NOR

- E) NOT

- **59**. Em iguais condições em termos de senóide de entrada, diodos, resistor e capacitor, pode-se esperar que o ripple seja:

- A) maior no conversor de meia onda, menor e iguais entre si nos conversores de onda completa e de ponte retificadora

- B) menor no conversor de onda completa, maior e iguais entre si nos conversores de meia onda e de ponte retificadora

- C) maior no conversor a ponte retificadora, menor e iguais entre si nos conversores de meia onda e de onda completa

- D) menor no conversor de meia onda do que no de onda completa, ambos menores do que no conversor de ponte retificadora

- E) maior no conversor de meia onda do que no conversor de ponte retificadora, ambos menores que no conversor de onda completa

- **60**. Pedidos de interrupções, exceções e DMA (acesso direto à memória) são serviços especiais de um computador. Eles são de natureza, respectivamente:

- A) síncrona / assíncrona / assíncrona

- B) síncrona / síncrona / assíncrona

- C) assíncrona / síncrona / síncrona

- D) assíncrona / assíncrona / síncrona

- E) síncrona / assíncrona / síncrona